Paging Subsystem

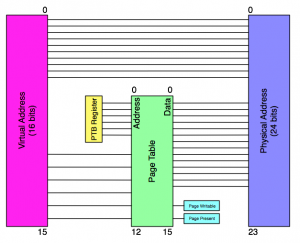

ECLair uses a 24-bit physical address space with 16-bit virtual addresses, and a paging system is used to translate between the two.

When the system starts up the PE (Paging Enabled) flag is set to zero, and virtual addresses are used directly, only allowing access to the first 64kb of ROM, and no RAM or device space (this PE=0 memory map may or may not change later as the design continues coming together).

When the PE flag is set to one, part of MAR is sent through the paging mechanism to be converted into a 24-bit address, allowing access to a large amount of memory, a small bit at a time.

- 64 page table blocks available in the page table

- Each block controls 64 pages

- Each page is 1K long

- Bit 15 (MSB) in page table entry is 1 if page is present

- Bit 14 in page table entry is 1 if page is writable

- Address Routing

- Virtual address – 16 bits

- Bits 15-10 – Page Select – passed to page table address bits 11-6

- Bits 9-0 – Address – passed to ADDR LSB as-is

- Physical address – 24 bits

- Bits 23-10 – Page – passed from page table data bits 13-0

- Bits 9-0 – Address – passed from virtual address bits 9-0

- Virtual address – 16 bits

Memory Map

- 24bit / 16MB address space

- 14MB for RAM, 1MB for ROM, 1MB for memory-mapped devices

- 0x000000 – 0x0FFFFF – ROM

- 0x100000 – 0xEFFFFF – RAM

- 0xF00000 – 0xFFFFFF – Devices