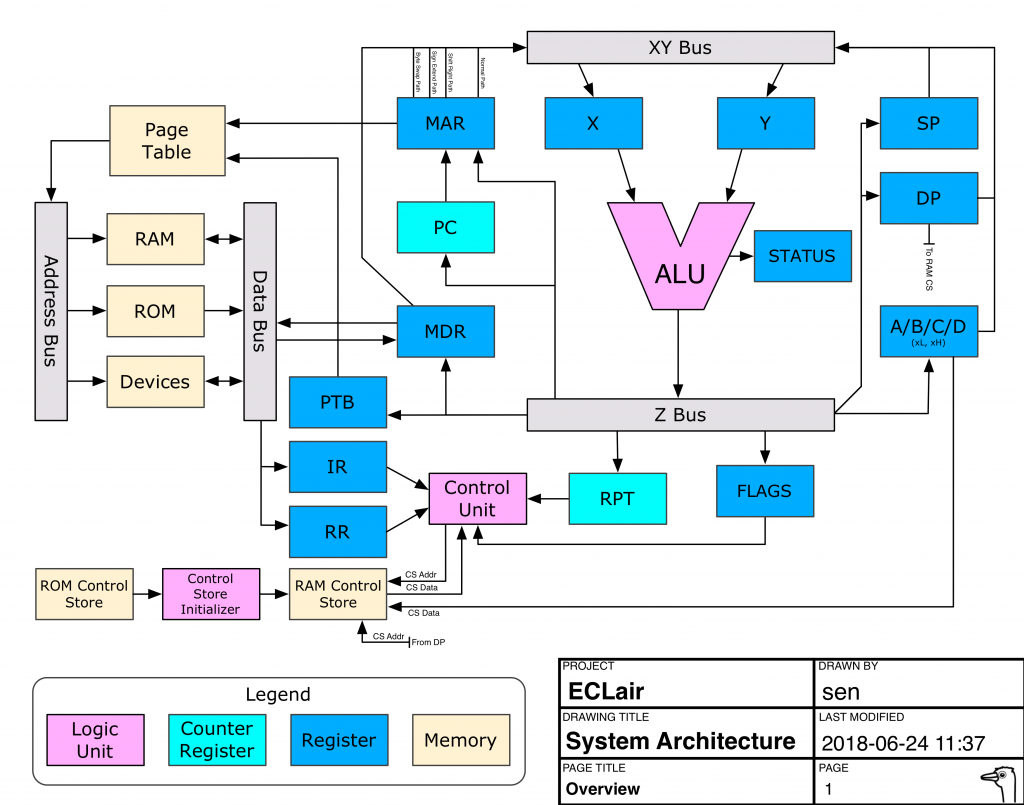

System Overview

ECLair is a microcoded CPU built with the ECL logic family. The system uses an 8-bit data bus, 16-bit general purpose registers (each of which can also be addressed as two 8-bit registers), a 24-bit physical address bus, and 16-bit virtual addresses.

The microcode is loaded from EPROM to control store RAM at system startup for performance reasons, and supports writing to microcode to extend the CPU with new or reworked instructions at runtime.

System Specifications

Widths

- Data Bus Width: 8 bits

- Address Bus Width: 24 bits

- Virtual Address Width: 16 bits

- Microcode Width: 64 bits

Registers

- 4 general purpose registers: 16 bits wide each

- Can also be addressed as 8 8-bit registers

- 2 memory access registers: 16 bits wide each

- 3 special user-accessible registers

- Several microcode-only registers for internal use

Memory

- 24-bit physical addresses, 16MB of address space total

- 1MB ROM

- 14MB RAM

- 1MB of space for memory-mapped devices

- All memory is addressed via the page table when the PE flag is on, allowing access to all 16MB via 16-bit addresses