Reworked cs_addr path

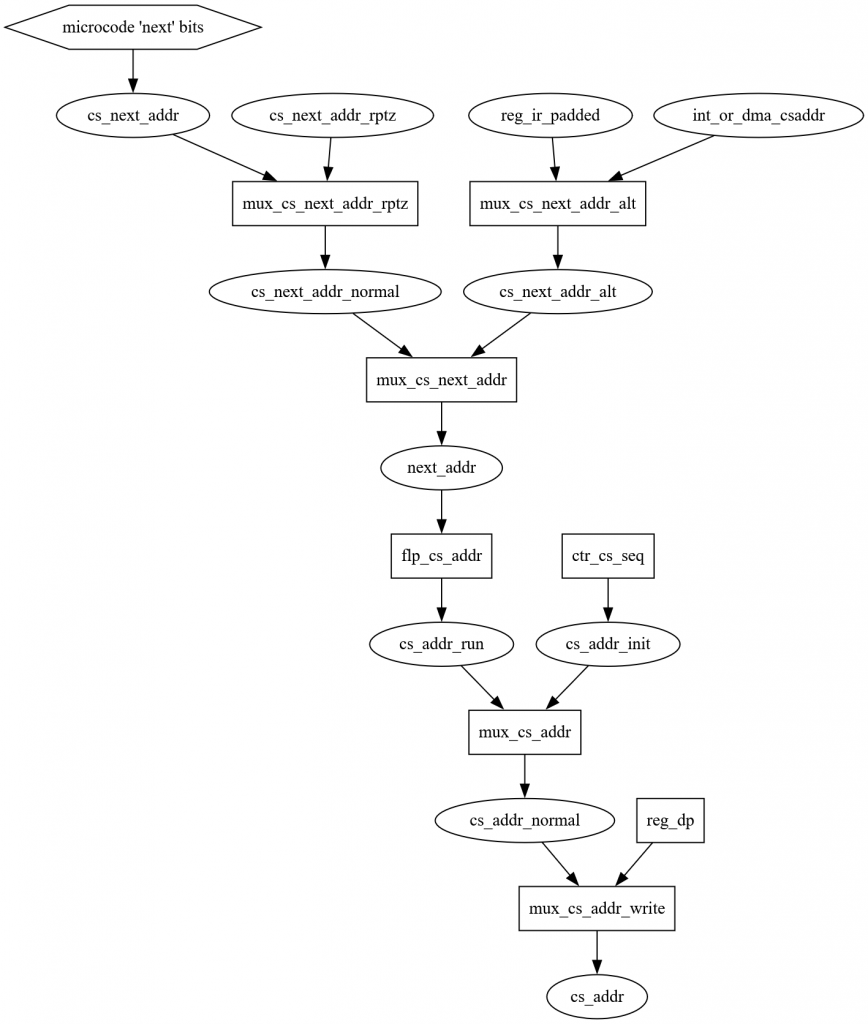

When I started working on page faults and exceptions in general, I realized that the path that cs_addr was flowing through had grown to the point where it wasn’t very maintainable, was excessively long for propagation, and was making troubleshooting harder. It initially just had a mux that selected either IR or the control store next_addr bits, but over time it had gained 4 more inputs, each via a chained 2:1 mux.

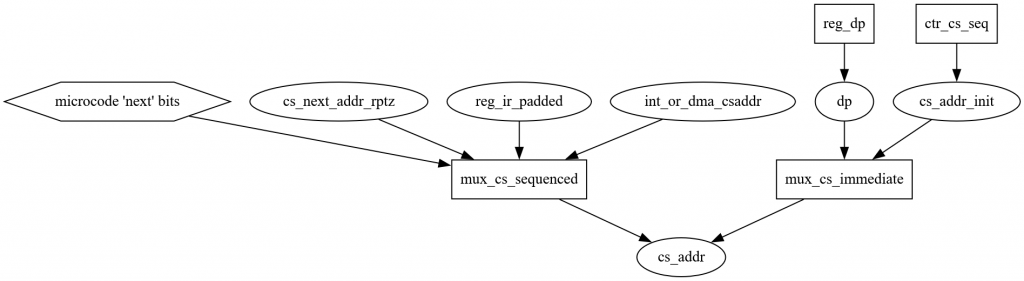

I reworked this to use two 4:1 muxes instead, and since the MC10E156 has a built-in latch, I was able to eliminate the separate latch as well. This design relies on the wired-OR ability of ECL much like the XY bus, with one mux or the other always being held in reset, and the outputs of the two just wired together.

In the end 12 chips were removed, 6 new ones added, about half an amp improvement made in current draw, and a few nanoseconds improvement on the propagation time of this signal. Plus this new design is a lot easier to understand and troubleshoot and it gives two spare inputs, one of which will get used for exceptions.